# VOICE OF THE ENGINEER

July Issue 14/2005 www.edn.com

Prying Eyes: Contactless traveling Pg 42

**Q&A:** Cisco's Todd Westerhoff on EDA Pg 26

Global Designer: WiCon, FPGAs, and more Pg 28

Design Ideas: Pg 85

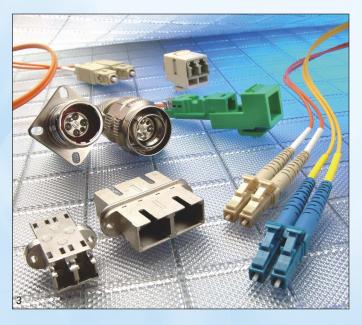

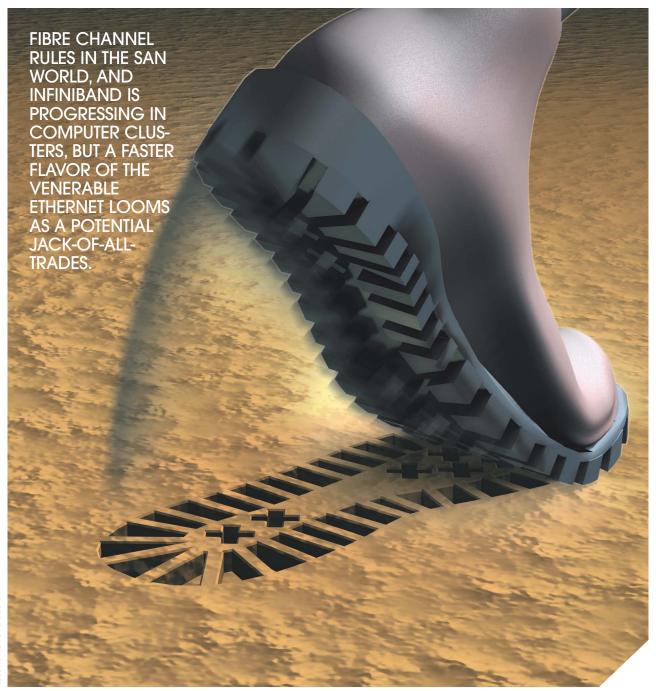

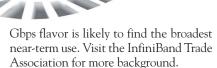

FIBRE CHANNEL, INFINIBAND, ETHERNET:

### WHICH INTERFACE WILL GET TRACTION?

Page 58

CAT5 TRACKS: AUDIO GOES THE DISTANCE, RELIABLY AND ON TIME Page 47

STRUCTURED ASICS DESERVE SERIOUS ATTENTION AT 90 NM Page 69

WINDOWED-WATCHDOG TIMERS ENHANCE SYSTEM SECURITY Page 79

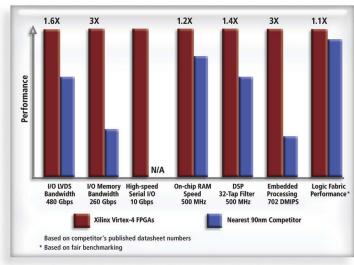

Virtex-4 beats competing FPGAs in every performance category

### Virtex-4 FPGAs beat the competition in EVERY performance category.

Only Virtex<sup>31</sup>-4 Platform FPGAs offer you superior performance in every aspect of a system. No other FPGA comes close to Virtex-4, which delivers a significant advantage in I/O bandwidth, on-chip RAM speed, DSP & processing compute bandwidth, and logic fabric performance. Having all the right features is the only way to achieve breakthrough performance at the lowest cost.

### THE WORLD'S FASTEST AND LOWEST POWER FPGAS!

Virtex-4 FPGAs also give you high performance without breaking your power budget, with significantly lower power consumption than competing 90nm FPGAs, 73% lower static power, up to 86% lower dynamic power, and 94% lower inrush current.

Visit our website today, and find out more about the *real* leader in FPGA performance.

### www.xilinx.com/virtex4/performance

Enter 1 at www.edn.com/info

BREAKTHROUGH PERFORMANCE AT THE LOWEST COST

**#1 for Breadth of Product Line!**

# Olfi-KEY IS THE LEADER WHEN IT COMES TO BREADIH OF PRODUCT LINE... offering access to nearly a half-million different part numbers from over 300 different quality, name-brand manufacturers! Digi-Key is truly your one-stop source for all your needs. Based on an independent survey of design engineers conducted by Beacon Technology Partners, LLC, of EE Times' readers, Digi-Key Corporation earned the highest scores from among hundreds of major U.S. distributors across numerous distinctive categories, including "Breadth of Product Line"! categories, including "Breadth of Product Line"! Source: EE Times Distributor Evaluation Study, August 2004

800.344.4539 · www.digikey.com · 218.681.3380

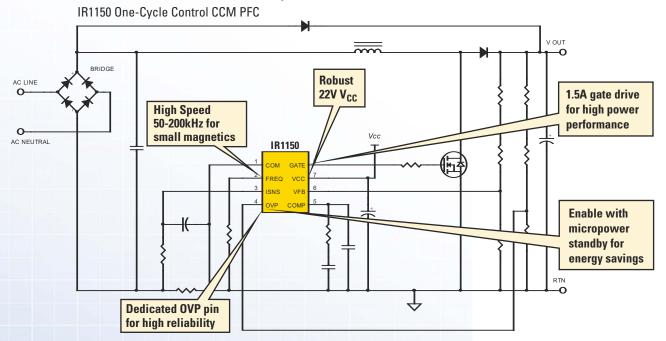

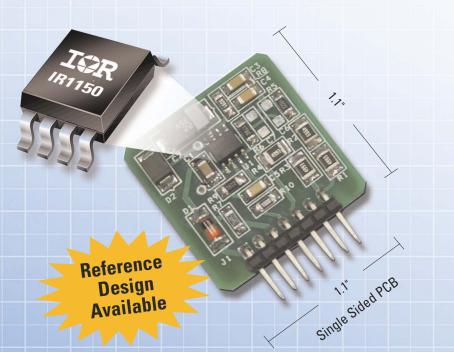

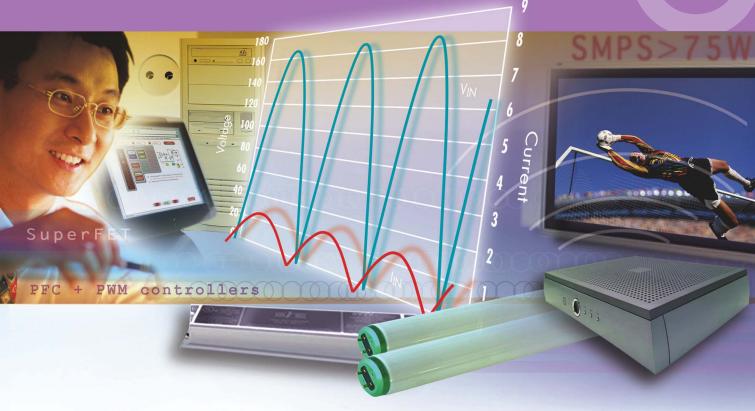

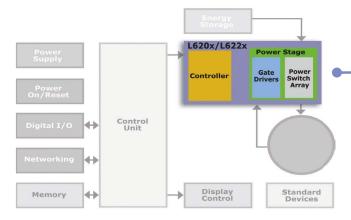

# **PFC:** SIMPLE, SMALL, POWERFUL

From 75W to 3kW+

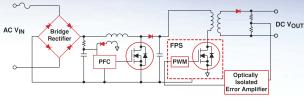

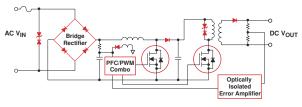

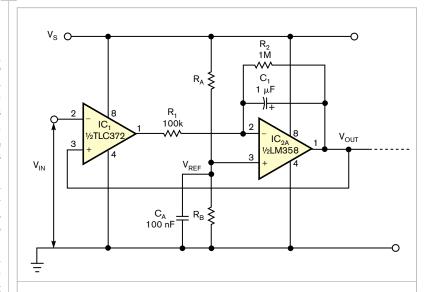

### TYPICAL CIRCUIT DESIGN USING µPFC™

for more information call 1.800.981.8699 or visit us at <a href="http://www.irf.com/acdc">http://www.irf.com/acdc</a>

Plug our new IR1150 μPFC into your design:

- Simplifies compliance with new energy efficiency and harmonic regulations

- · One-Cycle Control technique

- No AC-line sensing

- 50% less PCB area\*

- 40% fewer parts\*

- 45% fewer design steps\*

- SOIC-8 package

- · Enables bridge-less boost designs

\* in typical 1kW power supply  $\mu PFC^{TM}$  is a trademark of International Rectifier Corporation

Enter 3 at www.edn.com/info

International Rectifier

THE POWER MANAGEMENT LEADER

# With Atmel's AVR microcontrollers, your designs will always give you more than you expected.

If you're looking for ways to get better designs to market faster (and who isn't these days), start designing with Atmel's AVR® family of MCUs. No other 8-bit micro can give you

its exceptional combination of performance, flexibility and power management.

AVR is the most efficient and powerful 8-bit MCU on the planet. It has an enhanced RISC core running single-cycle instructions and a well-defined I/O structure that limits the need for external components. So it's not only easier to use, it delivers blazing execution of up to 20 MIPS.

And when you consider AVR's outstanding Flash and EEPROM capability, plus its huge range of packaging,

peripherals, memory sizes, power management modes and development tools, there's almost no limit to what you can design. From complex battery operated applications to industrial controls, and a whole lot more in between.

That's why AVR has become the most popular microcontroller of its kind, with over a billion installed around the world.

So if you're looking for ways to get more out of your designs, make sure you use the microcontroller that delivers more.

Check it out today at www.atmel.com/ad/avr and register to win a free development kit. It just could be the start of a very fruitful relationship.

### Find out more about Atmel's AVR solutions today at www.atmel.com/ad/avr

| Performance       | Up to 20 MIPS                                                            |  |

|-------------------|--------------------------------------------------------------------------|--|

| Power consumption | 100nA (power down)                                                       |  |

| Memory size       | 1 to 256 Kbytes Flash                                                    |  |

| Packaging         | 8 to 100 pins                                                            |  |

| Peripherals       | eripherals UART, SPI, 2-wire interface, timers, PWM, 10-bit AD, CAN, LCD |  |

| Migration path    | All devices code compatible for seamless upgrade                         |  |

### we'll help you design it.

Personal Media Player. People want to watch TV programs, movies and home videos on their own schedule. That's why today's personal media players allow people to access the content they love, whenever and wherever they want. At the core of this revolution in personalized content is the Philips Nexperia Media Processor, which makes it possible to record broadcast video, download and view movies from the Internet, and store or share digital photos. The processor allows you to attach the player to a TV for DVD video quality — even high-definition output. As an industry leader in media processing technology, Philips Semiconductors is prepared to be your partner in designing what's next.

- I. Media Processor/System Control Nexperia PNX I 500 Media Processor supports DivX, MPEG-2, MPEG-4, H.264, WMV9, motion adaptive de-interlacing, real-time DVD-quality MPEG-4 video encoding, and scaling as well as system control, UI, and communications.

- **2. Power Management Unit –** PCF50606 PMU+. One chip provides complete system power supply and management including DC/DC converters, battery management, charger control and dynamic power control that optimizes multiple voltage levels in real time to minimize power consumption.

- **3. TV Codec –** SAA7109 TV codec provides A to D and D to A conversion for composite video signals; decodes PAL, NTSC, SECAM, encodes PAL, NTSC and 720P, 1080I HD video out.

- 4. Wireless LAN 802.11g BGW211 System-in-a-Package (SiP) 802.11g solution features the industry's lowest standby and operating power consumption and supports 802.11e for enhanced QOS.

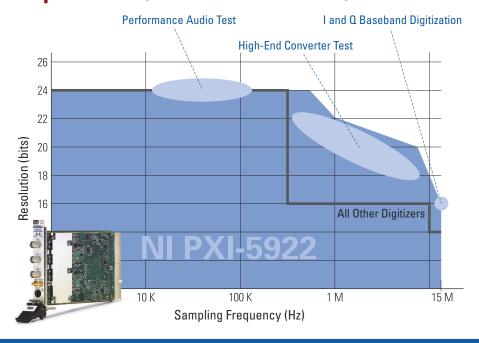

### **Industry's Highest-Resolution Digitizer**

### From 24 bits up to 500 kS/s to 16 bits at 15 MS/s

To view a seven-minute online demo of the NI PXI-5922, go to ni.com/modularinstruments.

(800) 449 6347 or ni.com

### **Discover the Signals You've Been Missing**

The new National Instruments PXI-5922 flexible-resolution digitizer uses patented techniques to deliver the highest resolution and highest dynamic range of any digitizer today up to 15 MS/s. The dual-channel digitizer features:

- Flexible resolution from 24 bits up to 500 kS/s to 16 bits at 15 MS/s

- · Spectral, audio, vibration, and communications analysis software

- -120 dBc typical SFDR and -120 dBFS rms noise

- Deep onboard memory up to 256 MB per channel

- Integrated antialias protection for all sampling rates

With innovative hardware capabilities and more than 400 measurement and analysis functions, the NI PXI-5922 revolutionizes dynamic measurements for user-defined applications. From DC to RF, NI modular instruments power measurements from prototype to production.

Define your test system with NI modular instrumentation.

| Multimeters            | 7½ digits, 1000 V                              |  |

|------------------------|------------------------------------------------|--|

| Audio Analyzers        | 24 bits, up to 500 kS/s                        |  |

| Digitizers             | 8-24 bits, up to 200 MS/s                      |  |

| Signal Generators      | Up to 16 bits, 200 MS/s                        |  |

| High-Speed Digital I/O | Up to 400 Mb/s                                 |  |

| RF                     | 2.7 GHz, 20 MHz RTB                            |  |

| Switching              | Multiplexers, matrices,<br>RF switches, relays |  |

| Multifunction I/O      | Analog input and output, digital I/O, counters |  |

© 2005 National Instruments Corporation. All rights reserved. NI and ni.com are trademarks of National Instruments.

Other product and company names listed are trademarks or trade names of their respective companies.

# EDN contents 7,7,05

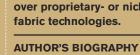

### Which interface will get traction?

Fibre Channel rules in the SAN world, and InfiniBand is progressing in computer clusters, but a faster flavor of the venerable Ethernet looms as a potential jack-of-alltrades.

by Maury Wright, Editor at Large

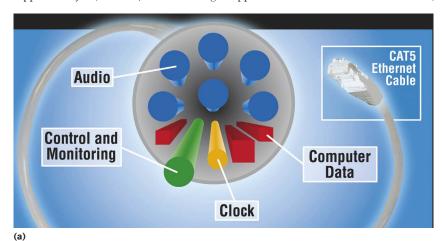

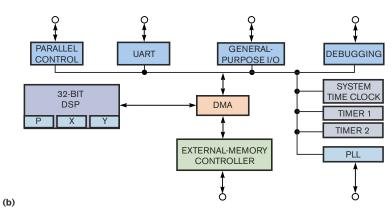

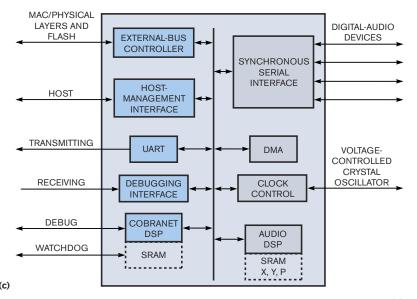

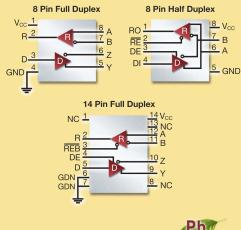

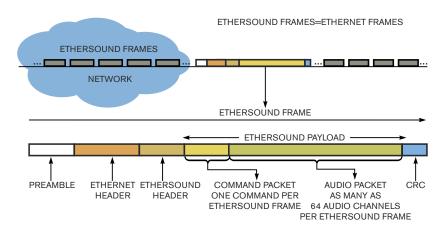

### CAT5 tracks: Audio goes the distance, reliably and on time

Do you want to route high-bit-rate digital audio over long expanses with minimal latency and "five-nines" reliability? Find out whether a conventional Ethernet scheme will meet your needs or whether you need an audio-optimized variant. by Brian Dipert, Technical Editor

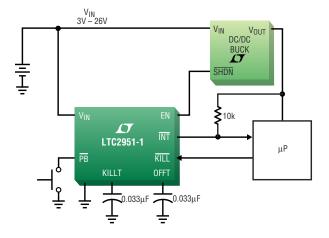

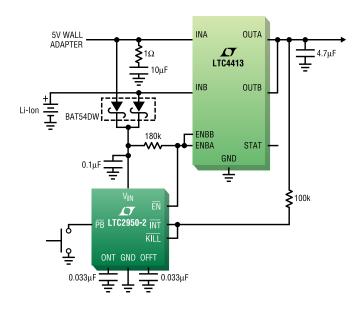

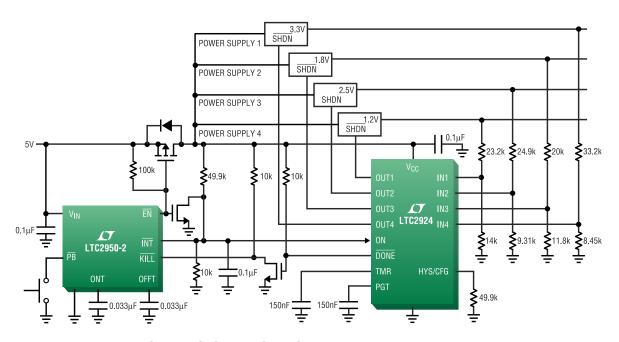

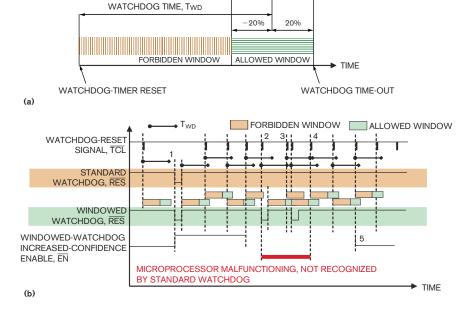

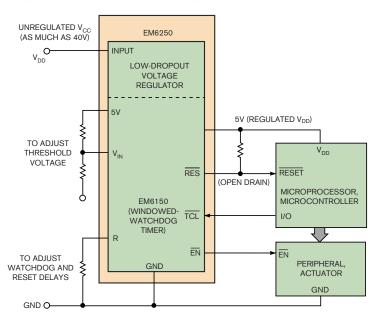

Windowed-watchdog timers enhance system security

A supervisory function enables system recovery to prevent execution errors.

> by Donald W Corson, EM Microelectronic

### DESIGNIDEAS

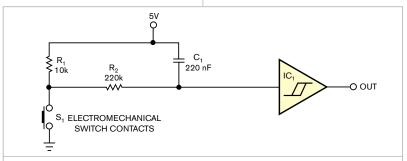

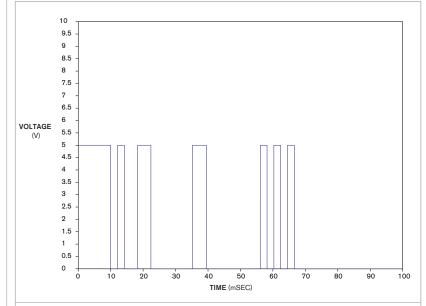

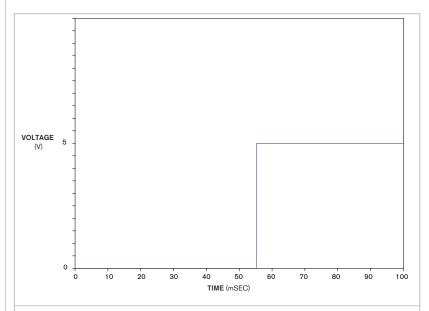

- 85 Contact-debouncing algorithm emulates Schmitt trigger

- 88 Inexpensive peak detector requires few components

- 94 Free program designs and analyzes passive and active filters

### Users should take a long, hard look at structured ASICs when considering which fabric to use for their next logic

Structured ASICs

deserve serious attention at 90 nm

by Michael Santarini, Senior Editor

The cost of 90-nm-not

to mention 65-nm-

silicon is outrageous.

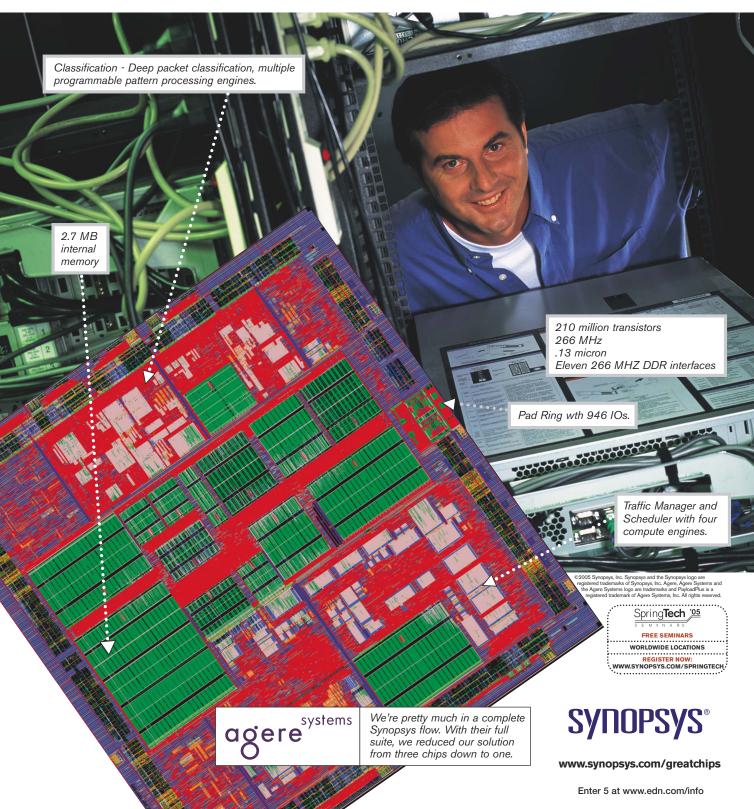

## "It not only reduces cost, it makes that old network equipment feel young again."

Roger Bailey / Senior Technical Manager, Agere Systems

### contents 7.7.05

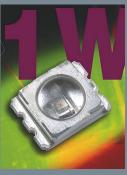

- 19 Intense LEDs take on the sun

- 19 Book leads those on the digital dark side to the analog force

- 19 Simple transformer monitors ac currents

- 20 Track-and-hold device allows direct capture of signals greater than 10 GHz

- 20 LED module delivers 60 lumens

- 22 Tool analyzes ICs

- 22 Embedded DSP simplifies programming

- 22 Physical guide routes optical guide

- 24 Emulators speed event-based verification

- 24 Module enables graphical embedded programming

- 26 Q&A: Cisco's Todd Westerhoff on EDA

- 28 **Global Designer:** WiCon panel opines on state of wireless standards, FPGAs implement high-end image-processing applications, bits & pieces

### DEPARTMENTS & COLUMNS

- 12 **EDN.comment:** Are we losing our innovation religion?

- 32 Baker's Best: One in a million

- 42 **Prying Eyes:** Contactless traveling

- 102 Reality Check: Robot vacuum cleaner cleans up in many ways

### PRODUCT ROUNDUP

96 Passives, Integrated Circuits, Microprocessors

EDN ® (ISSN#0012-7515), (GST#123397457, R.B.I. Intl Pub Mail #0280844) is published biweekly, 26 times per year, by Reed Business Information, 8878 Barrons Blvd, Highlands Ranch, CO 80129-2345. Reed Business Information, a division of Reed Elsevier Inc, is located at 360 Park Avenue South, New York, NY 10010. Jim Casella, Chief Executive Officer; Stephen Moylan, President, Boston Division. Periodicals postage paid at Littleton, CO 80126 and additional mailing offices. Circulation records are maintained at Reed Business Information, 8878 Barrons Blvd, Highlands Ranch, CO 80129-2345. Telephone (303) 470-4445. POSTMASTER: Send address changes to EDN ®, PO Box 7500, Highlands Ranch, CO 80163-7500. EDN ® copyright 2005 by Reed Elsevier Inc. Rates for nonqualified subscriptions, including all issues: US, \$149.90 one year, Canada, \$205.90 one year, (includes 7% GST, 651#123397457); Mexico, \$185.90 one year; air expedited, \$361.90 one year. Except for special issues where price changes are indicated, single copies are available for \$10.00 US and \$15.00 foreign. Publications Mail Agreement No. 40685520. Return undeliverable Canadian addresses to: Deutsche Post, 4960-2 Walker Road, Windsor ON N9A 6J.3. E-mail: subsmail@reedbusiness.com. Please address all subscription mail to EDN ®, 8878 Barrons Blvd, Highlands Ranch, CO 80129-2345. EDN ® is a registered trademark of Reed Elsevier Properties Inc, used under license. A Reed Business Information Publication/Volume 50, Number 14 (Printed in USA)

### **EDN** ONLINE

### **Express yourself**

In line with our new motto—Voice of the Engineer—we're providing more opportunities than ever for you to share information and opinions with your peers at www.edn.com.

→ Feedback Loop: An online bulletin board that allows you to post comments on a specific article. Look for it on the left side of every article on the site. See a list of all the active threads at www.edn.com/feedbackloop, and check out the ongoing discussions on these recent articles:

### Embedded-system programmers must learn the fundamentals

www.edn.com/article/CA601846

### Baker's Best: Turning Nyquist upside down by undersampling

www.edn.com/article/CA529378

→ Blogs: Discussions that our editors lead:

**Brian's Brain,** by Brian Dipert www.edn.com/briansbrain

Recent topics: Advanced video codecs, gadgets for the road, dual-core processors

On The Verge, by Maury Wright www.edn.com/ontheverge

Recent topics: Podcasts go mainstream, Wi-Fi hurts cafés, Zigbee products roll

### Only on www.edn.com

### EDN readers list engineering heroes

When Editor in Chief John Dodge asked you to name your engineering heroes in a recent column, he clearly hit upon something you were eager to talk about.

www.edn.com/article/CA607116

### DAC-stravaganza

An archive of news coverage from the recent Design Automation Conference.

www.edn.com/article/CA607973

### Free Webcast features *EDN* Editorial Advisory Board member Chuck Clark Jr

As a Boeing Technical Fellow, holder of 15 patents, and survivor of nine takeovers in the electronics and aerospace industries, Chuck Clark has developed some interesting insights into engineering. *EDN* Editor in Chief John Dodge interviewed Clark in a recent online conference.

http://e2e.unisfair.com/

### PCI-SIG forms I/O virtualization specification group

Virtualization extensions to the PCI Express standard would define a standardized method for a single physical device to present itself to a system as multiple virtual devices.

www.edn.com/article/CA608868

series has culminated in 📭 coercive force of 398kA/m 📭 coercive force temperature coefficient of 0.18kJ/m 📭 residual flux density of 460mT

the history of ferrite magnet technology. But this is not the end, this is the first step on a new journey for the <FB9> series, and we can see an ever

um energy product of 40.4kJ/m³. It is the extraordinary TDK magnetic technology that has enabled this unprecede

higher peak to conquer. Be prepared for something even better, you can count on the next generation of TDK.

70 years at the edge. TDK

http://www.component.tdk.com/

Enter 6 at www.edn.com/info

**公TDK**

tdk.com/

Ferrite magnets have reached a new world peak of performance\*.

⊗TDK is a trademark or registered trademark of TDK Corpora

### BY BILL SCHWEBER, EXECUTIVE EDITOR

### Are we losing our innovation religion?

f you really want to worry about the state of our industry—for both our engineers and our companies—pick up a copy of the March 21, 2005, Business Week, which is available free online with registration or at your local library. The multifaceted cover story "Outsourcing Innovation" filled in the details with examples and numbers of what many of us already know or have heard: Not only engineering-design roles, but also all of the functions—the very essence of many companies—are "going away." We are helping them to evaporate.

This issue is not about simple globalization. Globalization itself—locating your staff worldwide to take advantages of various perceived attributes they offer, for both technical expertise and lower cost—is unavoidable given the time, cost, complexity, and pressures of today's designs. Also, globalization provides an around-the-clock advantage and the technology-enabled ease of transferring data and designs from Point A to Point B.

But why stop there, many companies are asking? You can outsource product design to a third party, which in turn may use big chunks of external IP (intellectual property); you can outsource physical manufacturing; and now, you can even outsource your research and development. The article gave plenty of examples of which companies are using this approach and the results in apparent cost (read "people")

# Outsourcing innovation starts a dangerous downward spiral.

savings. What's left? Not to worry, many say: The companies that outsource so many aspects of their roles can do the upfront product definition, as well as the product marketing. Sounds like a plan, doesn't it?

However, all this outsourcing buries a reality: Once your outsource partners learn how you define products, how you market them, and whatever other "secret" understanding you have or you assume that you have, and you have an "in" on your markets, those partners no longer need you. It's that simple. The "secret sauce" you think makes a difference may not be such a secret or

maybe isn't the barrier to entry that you thought it was.

You already see this entry of new players in diverse markets, such as home appliances and consumer products. In these markets, companies most of us have never heard of are using widely available chip sets and components and quickly developing a significant presence in the markets of longestablished market leaders.

If a company thinks it can survive and remain a market force if it just does marketing and branding, while abandoning true R&D, design, and innovation, the company is deluding itself. The shelves of Wal-Mart are full of brands that used to be real players and now exist only as nameplates.

Remember RCA? Once the undisputed leader in TV innovation, the company spent more than a billion in 1950s' dollars to develop color TV as we know it today, including architecture, CRTs, imagers, and much more. Then, in addition to its other corporate missteps, such as going to conglomerate mode and supplying home appliances, carpets, rental cars, and more, it began the process of shedding. It outsourced the labor-intensive soldering of the wired TV chassis that predate pc boards, albeit using US-sourced components. Next, the manufacturing of these components—mostly passives—moved; then, the design of these components traveled. Next came manufacturing of the more complex parts; then, their design; and, soon, all that was left was an empty shell of a well-respected brand, and a name that used to have distinctive value—but now had none.

When your functions and true added value have atrophied by that magnitude, anyone can step in and take away your markets, shelf space, and business. Today's smart move to outsourcing almost everything may be the dumbest long-term move a company can make.EDN

### MORE AT EDN.COM

$\triangleright$

Go to www.edn.com/article/

CA601510 and click on Feedback Loop

to post a comment on this column.

### device characterization • parametric I-V analysis • stress-measure • reliability tests • device modeling • materials research

The Model 4200-SCS, the industry's most popular and productive parametric analyzer, is now your best choice for reliability testing, too. New stress-measure capabilities in our 5.0 software release simplify testing. Exceptional current sensitivity (to 100 attoamps) and an intuitive Windows XP® interface make the Model 4200-SCS the best, most cost-effective solution for a growing list of applications:

- Semiconductor technology development

- Incoming inspection, failure analysis

- Device reliability and lifetime testing

- Nanotechnology research

- $\blacksquare$  High and low κ dielectrics

- Organic LEDs

- Hall Effect and Van der Pauw testing

- Semiconductor process integration

- RFIC, high power MOSFET/BJT

For a demo, contact us at 1-800-588-9238 or for more information, visit www.keithley.com/at/173.html

A GREATER MEASURE OF CONFIDENCE

Enter 7 at www.edn.com/info

### **Inside The Best, You'll Find Micrel!**

From Cable and DSL routers to telephones and media players, the very best Ethernet-enabled products choose Micrel's KS-series switches and routers. That's because Micrel's leading-edge switches come with world-class customer support, extremely competitive pricing and zero defects quality:

- World class support means responsive, knowledgeable support anywhere in the world that our customers need us to be

- Competitive pricing means the very best cost possible

- And to Micrel, quality is simple; it means no excuses, no mistakes, no failures, period

Our dedication to support, competitive pricing and quality also means that our customers' consistently win Editor's Choice awards and other industry accolades for their outstanding products. That's because outstanding products use the very best switches inside; Micrel switches.

Visit our website to learn more about our outstanding family of switches and other Ethernet products: www.micrel.com/ad/ethernet.

Literature: 1 (800) 401-9572

Factory: 1 (408) 944-0800 Stocking Distributors: Arrow 1 (800) 777-2776

> Future 1 (800) 388-8731 Newark 1 (800) 463-9275 Nu Horizons 1 (888) 747-6846

#### PRESIDENT, BOSTON DIVISION/ PUBLISHING DIRECTOR, **EDN** WORLDWIDE

Stephen Moylan, 1-781-734-8431; fax: 1-781-290-3431; smoylan@reedbusiness.com

### EDITOR IN CHIEF

John Dodge, 1-781-734-8437; fax: 1-781-290-3437; john.dodge@reedbusiness.com

### EDITOR AT LARGE

Maury Wright, 1-858-748-6785 mgwright@edn.com

#### **EXECUTIVE EDITOR**

Bill Schweber, 1-781-734-8447; fax: 1-781-290-3447; bschweber@edn.com

### ASSISTANT MANAGING EDITOR

Kasey Clark, 1-781-734-8436; fax: 1-781-290-3436; kase@reedbusiness.com

### EXECUTIVE EDITOR, ONLINE

Matthew Miller, 1-781-734-8446; fax: 1-781-290-3446; mdmiller@reedbusiness.com

#### SENIOR ART DIRECTOR

Mike O'Leary, 1-781-734-8307; fax: 1-781-290-3307; moleary@reedbusiness.com

#### EMBEDDED SYSTEMS

Warren Webb, Technical Editor 1-858-513-3713; fax: 1-858-486-3646 wwebb@edn.com

#### ANALOG/COMMUNICATIONS, DISCRETE SEMICONDUCTORS

Joshua Israelsohn, Technical Editor 1-781-734-8441; fax: 1-781-290-3441 iisraelsohn@edn.com

### EDA, MEMORY, PROGRAMMABLE LOGIC

Michael Santarini, Senior Editor 1-408-345-4424 michael.santarini@reedbusiness.com

#### MICROPROCESSORS, DSPs. TOOLS

Robert Crayotta, Technical Editor 1-661-296-5096; fax: 1-781-734-8070 rcravotta@edn.com

### MASS STORAGE, MULTIMEDIA.

PERIPHERALS, AND PC-CORE LOGIC

Brian Dipert, Technical Editor: 1-916-760-0159 fax: 1-781-734-8070; bdipert@edn.com

### POWER SOURCES, ONLINE INITIATIVES

Margery Conner, Technical Editor; 1-805-461-8242; fax: 1-805-461-9640; mconner@connerbase.com

### **DESIGN IDEAS EDITOR**

Brad Thompson

### edndesignideas@reedbusiness.com

SENIOR ASSOCIATE EDITOR Frances T Granville, 1-781-734-8439; fax: 1-781-290-3439; f.aranville@reedbusiness.com

### ASSOCIATE EDITOR

Maura Hadro Butler, 1-908-928-1403; mbutler@reedbusiness.com

### WEB/CPS PRODUCTION COORDINATOR

Contact for contributed technical articles

Heather Wiggins, 1-781-734-8448; fax: 1-718-290-3448; hwiggins@reedbusiness.com

### EDITORIAL AND ART PRODUCTION

Diane Malone, Manager; 1-781-734-8445 fax: 1-781-290-3445 Steve Mahoney, Production Editor 1-781-734-8442; fax: 1-781-290-3442 Adam Odoardi, Prepress Manager 1-781-734-8325; fax: 1-781-290-3325

### **NEWS EDITOR**

Jeff Berman, 1-781-734-8449; fax: 1-781-290-3449; jeff.berman@reedbusiness.com

### CONTRIBUTING TECHNICAL EDITOR

Dan Strassberg, strassbergedn@att.net

#### COLUMNISTS

Ron Mancini: Howard Johnson, PhD: Bonnie Baker

#### PRODUCTION

Dorothy Buchholz, Group Production Director

1-781-734-8329 Kelly Brashears, Production Manager 1-781-734-8328; fax: 1-781-734-8086 Linda Lepordo, Production Manager 1-781-734-8332; fax: 1-781-734-8086 Pam Boord, Advertising Art 1-781-734-8313; fax: 1-781-290-3313

#### **EDN EUROPE**

Graham Prophet, Editor, Reed Publishing The Quadrant, Sutton, Surrey SM2 5AS +44 118 935 1650; fax: +44 118 935 1670; gprophet@reedbusiness.com

#### EDN ASIA

Raymond Wong, Managing Director raymond.wong@rbi-asia.com Kirtimaya Varma, Editor in Chief kirti.varma@rbi-asia.com

#### EDN CHINA

William Zhang, Publisher and Editorial Director wmzhang@idg-rbi.com.cn John Mu, Executive Editor johnmu@idg-rbi.com.cn

#### EDN JAPAN

Katsuya Watanabe, Publisher k.watanabe@reedbusiness.jp Kenji Tsuda, Editorial Director tsuda@reedbusiness.jp Tsuguyuki Watanabe, Editor in Chief t.watanabe@reedbusiness.jp

The EDN Editorial Advisory Board serves as an industry touchstone for the editors of EDN worldwide, helping to identify key trends and voicing the concerns of the engineering community.

### **DENNIS BROPHY**

Director of Business Development, Mentor Graphics

### DANIS CARTER

Principal Engineer, Tyco Healthcare

CHARLES CLARK Technical Fellow, The Boeing Company

### DMITRII LOUKIANOV

System Architect, Intel RON MANCINI

Staff Scientist, Texas Instruments

### GABRIEL PATULEA

Design Engineer, Cisco

### MIHIR RAVEL

VP Technology, National Instruments DAVE ROBERTSON

Product Line Director, Analog Devices

### SCOTT SMYERS

VP Network and System Architecture Division, Sony

### TOM SZOLYGA

Program Manager, Hewlett-Packard

### JIM WILLIAMS

Staff Scientist, Linear Technology

EDN. 225 Wyman St. Waltham, MA 02451, www.edn.com, Phone 1-781-734-8000; fax: 1-781-734-8070. Address changes or subscription inquiries: phone 1-800-446-6551; fax: 1-303-470-4280; subsmail@reedbusiness.com. For a free subscription, go to www.getfreemag.com/edn. Reed Business Information, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. Include your mailing label.

### For superior solutions: NTC and PTC thermistors

- Application-specific designs

- High reliability

- Long service life

- Low cost

More information at www.epcos.com

Enter 9 at www.edn.com/info

just everywhere...

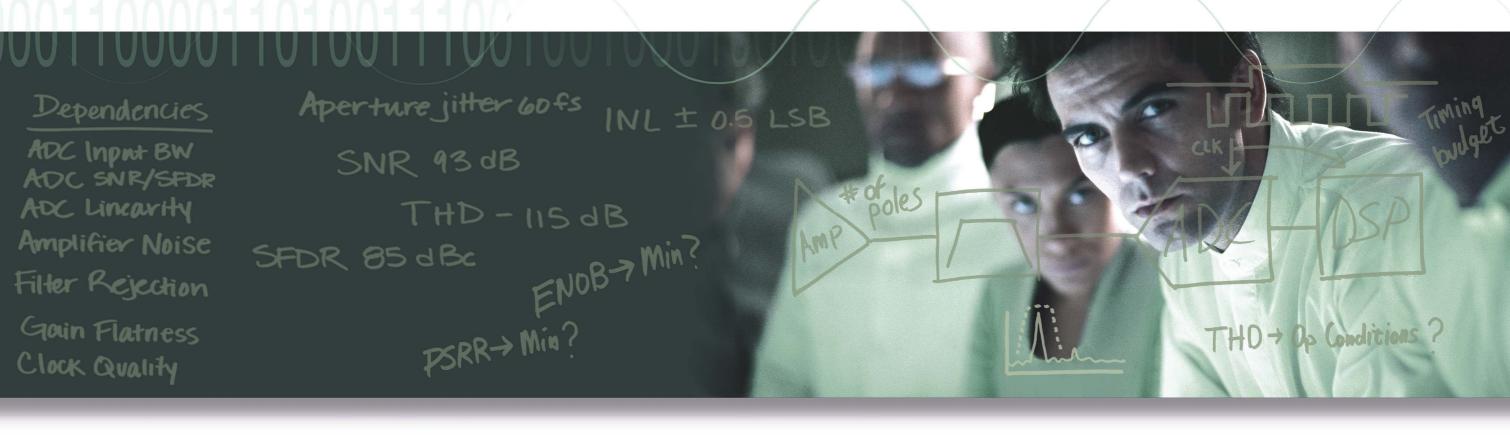

### Breakthrough data converter performance beyond speed and bits.

### **Highest performance ADCs...**

AD9445

14 bits, 125 MSPS 80 dBc SFDR @ 300 MHz 60 fs aperture jitter

**Base Station**

16 bits, 100 MSPS 80 dBc SNR 90 dBc SFDR

AD7621

16 bits, 3 MSPS ±1 LSB INL 90 dB SNR

Instrumentation

AD7641

18 bits, 2 MSPS ±2 LSB INL 93 dB SNR

AD7760

24 bits, 2.5 MSPS -100 dB THD100 dB to 118 dB SNR

Data Acquisition

... where it matters most.

### The performance levels that define your design

In the world of data conversion, more bits are good, and faster sample rates are even better. But good performance in one area is of little value if it comes with compromises in other areas, like ac linearity, dc accuracy, power consumption, integration, packaging, or price. Today, benchmark converters are about delivering leading performance on multiple levels and giving designers the combination of features they need for their particular applications. Like best-in-class nonlinearity for medical designs (AD7641), unparalleled SFDR for base stations (AD9445), or a combination of precision and small size (7 mm × 7 mm) for portable instruments (AD7621)—and of course, all with best-in-class speed and resolution to start.

Just because your design is complex does not mean you have to settle for trade-offs. More engineers are trading up to the levels of performance available only from Analog Devices. They know that when performance defines their design, they want the converters that define performance. For more information, please visit our website

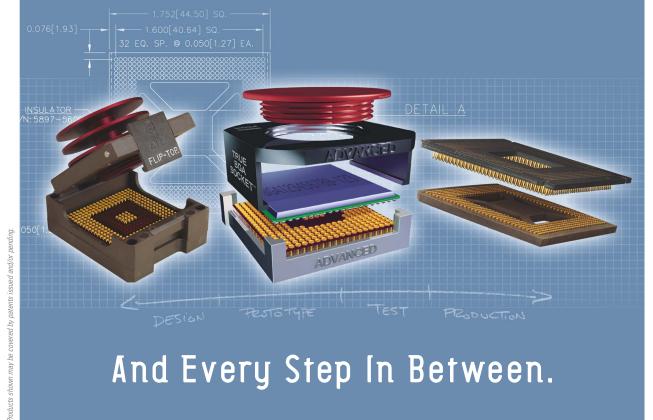

And Every Step In Between.

From concept to completion, Advanced is your single source for comprehensive BGA socketing systems. We specialize in economical, dependable alternatives to direct device attach, with an array of innovative solutions for any stage of development. Whether you're using BGA, LGA or CSP devices in prototype or production applications — you can be sure we're with you every step of the way.

To learn more, visit us online at http://www.bgasockets.com or call 1.800.424.9850.

5 Energy Way, West Warwick, Rhode Island 02893 USA

### Intense LEDs take on the sun

LEDs are moving up the intensity scale for outdoor-signage uses, as the OVL series demonstrates. The devices are available in a range of colors and 3-, 4-, and 5-mm sizes.

ccording to Richard Saffa, vice president of visible LEDs at Optek Technology, the company's OVL series of LEDs performs in full sunlight for a variety of display and signage applications, including commercial outdoor advertising. The through-hole, oval LEDs, in 3-, 4-, and 5-mm sizes, are available in blue, green, red/orange, and red with intensities that vary depending on color and size. For example, the 5-mm, red, AllnGaP device has typical intensity of 950 mcd at 20 mA, and the green InGaN device has an intensity of 1750 mcd.

Viewing angle also depends on size; representative viewing angle is 50° at half-power and 110° maximum. Power dissipation for these 25-cent devices is approximately 130 mW.—by Bill Schweber

**○Optek Technology**, www.optekinc.com.

### Book leads those on the digital dark side to the analog force

A familiar name to *EDN* readers, Bonnie Baker takes many of the subjects and themes of her popular "Baker's Best" column into more detail and depth in *A Baker's Dozen: Real Analog Solutions for Digital Designers* (Newnes/Elsevier, ISBN 0-7506-7819-4, May 2005). This clearly written, highly readable book explains both basic topics, such as A/D-converter operation, and the dilemmas that designers face, such as where, when, and how to filter signals in the signal-processing chain. Other topics include the use and validity of Spice models; digital-versus-analog-processing trade-offs and cooperation; and noise, layout, and grounding.

The \$59.95, 368-pg paperback devotes a chapter to the all-important topic of trouble-shooting mixed-signal designs. Colleges don't teach this subject, but engineers usually teach themselves at the debugging bench at first using bad judgment, which leads to ex-

perience and then to good judgment. This self-teaching primer will enhance your design, decision, and debugging skills so that you can face the reality of mixed-signal systems or digital designs with their inevitable analog-world aspects.—by Bill Schweber Newnes/Elsevier, http://books.elsevier.com.

### **FEEDBACK LOOP**

"Did I read that right? You can program the DSP directly in Visual Basic? Somebody actually built a VB compiler that generates native DSP code? What's next? Programming a DSP in Cobol?"

Ken Dyck, in *EDN*'s Feedback Loop on www.edn.com/article/CA605784. Add your comments.

### Simple transformer monitors ac currents

Is there an electrical component as versatile as the venerable transformer in its various manifestations? For measuring ac current, the 5600 series from C&D Technologies combines isolation to 500V with primary current rating to 10A. The device finds use in switched-mode power-supply feedback loops, motorcurrent monitoring, and other sensing applications. Bandwidth is 20 to 200 kHz, and these transformers are available in 50-. 100-, 200-, or 300-turn versions, for different sensitivity factors. Internal inductance is 5 to 335 mH, and dc resistance ranges from 117 m $\Omega$  to 8.6 $\Omega$ .

The less-than-\$1 units are available as two-lead and center-tapped devices and measure  $16.8 \times 20 \times 8.9$  mm.

—by Bill Schweber **C&D Technologies Inc,** www.cd4power.com.

The 5600 current-sensing transformer series offer 500V-dc isolation in 50- to 300-turn versions.

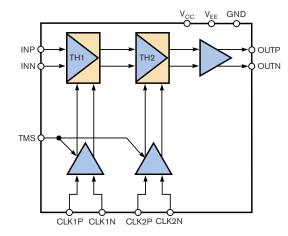

# Track-and-hold device allows direct capture of signals greater than 10 GHz

he extremely wideband RTH050 dual trackand-hold device from Rockwell Scientific enables direct conversion of gigahertzrange signals and signal edges with rise times of approximately 20 psec. This unit has small-signal input bandwidth of 15 GHz and supports a sampling rate of 100 to 1000M samples/sec. The differential signal-path device incorporates cascaded trackand-hold circuits to provide a hold time that is greater than one-half the clock cycle, which reduces bandwidth requirements for the subsequent signal-handling chain. Aperture jitter is 100 fsec, and acquisition time is 200 psec. Holdmode distortion is -42 dB for a 5-GHz signal with 0.5V p-p amplitude, rising to -30 dB for a 7.5-GHz signal; noise is less than 1 mV. Spurious-free dynamic range is 65 dB with a 1.060-GHz, 0.5V p-p signal.

According to Ron Latreille, product-line manager for mixed-signal products, the improved speed of this unit, compared with its predecessors, allows users "to digitize a broader range of signals with no increase in power con-

sumption" at 1.65W. A similar device, the RTH055, also integrates 12-dB attenuators to eliminate the need for external

components to scale down signals with excessive full-scale magnitude. The RTH050 sells for \$300 (100) and is available in a 13-lead HSD package.—by Bill Schweber Rockwell Scientific Co LLC, www.rockwellscientific. com.

Simple in concept but fast in execution, the RTH050 track-and-hold device from Rockwell Scientific offers a 15-GHz bandwidth and a 1G-sample/sec sampling rate with a dual internal structure for relaxation of interface timing.

### - FEEDBACK LOOP

"The Nyquist Theorem addresses avoiding aliasing of a reconstructed signal, not perfectly reconstructing the original signal. For signals approaching one-half the Nyquist frequency, severe amplitude attenuation periodically occurs as the sampled points move into and out of phase with the signal."

Konrad Kratz, in *EDN*'s Feedback Loop on www.edn.com/article/CA529378. Add your comments.

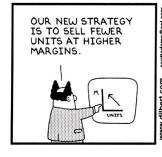

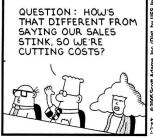

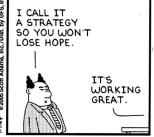

### **DILBERT** By Scott Adams

### LED module delivers 60 lumens

BivarOpto's LK series encompasses single-chip, 1W LEDs targeting safety, signaling, emergency, and general illumination. The 465- to 635-nm surface-mount devices, also available in white to 8000K, use a Cree XLamp die that includes an aluminum pcboard base for managing thermal issues. The lead-free encased met-

The LK Series of 60-lumen LEDs use a metal-core pc-board assembly to yield a 1W SMT design with integrated lens.

al-core module, which measures 20.3 mm sq, includes an integral lens; you can also get a two-pin header-based connector for snap-in and ease of replacement. The LED operates from -30 to +100°C; maximum forward current is 400 mA. The LK series modules sell for \$4 (volume quantities).

–by Bill Schweber BivarOpto, www. bivar.com.

### **Triple Supply Powers Spartan™-3**

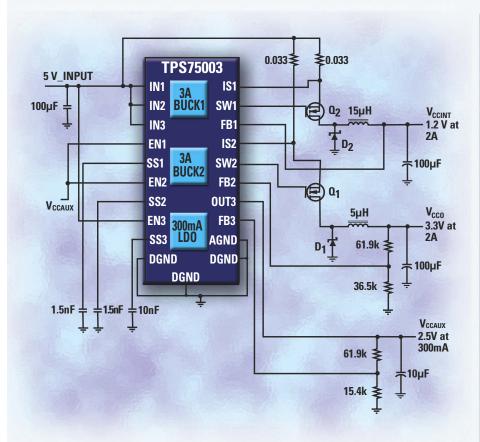

The **TPS75003** power management IC for Xilinx's Spartan™-II/IIE/3 series of FPGAs integrates multiple functions to significantly reduce the number of external components required and simplify design. Combining increased design flexibility with cost-effective voltage conversion, the IC includes programmable soft-start for in-rush current control and independent enables for sequencing the three channels. The TPS75003 meets all Xilinx startup profile requirements, including monotonic ramp and minimum ramp times.

### Applications

- DSL modems

- Set-top boxes

- Plasma TV display panels

- DVD players

### **▶** Features

- Two 95%-efficient, 3-A buck controllers and one 300-mA LDO

- Adjustable output voltages

- from 1.2 V for bucks

- from 1.0 V for LDO

- Input voltage range of 2.2 V to 6.5 V

- Independent soft-start for all three power supplies

- LDO stable with small ceramic output capacitor

- Independent enable for each supply for flexible sequencing

- 4.5 mm x 3.5 mm x 0.9 mm

20-pin, QFN package

- \$1.90: 1 K price

For more information on TI's complete line of power management solutions for Xilinx FPGAs—including a library of reference designs, schematics and BOMs—visit www.ti.com/xilinxfpga-u.

www.ti.com/xilinxfpga-u o 800.477.8924, ext. fpga

### Tool analyzes ICs

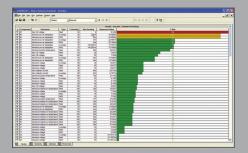

iga Scale Integration claims that its new ICeconomic-analysis tool can help you figure out whether a foundry's less expensive, standard 90-nm process or even its 130-nm process will meet your design reguirements just as well as the same foundry's pricier, lowpower, 90-nm process. The technology expands on the company's InCyte chip-estimation tool, which allows users to derive an IC specification with estimates on die size, power, performance, and leakage. The company has now taken the estimation technology a step further by creating an economic analysis add-on engine to InCyte that allows users to turn their design specification into an IC budgetary quotation and figure out the best foundry and fabric for their next design project.

Adam Traidman, Giga Scale IC's president and chief executive officer, says that the company gathered silicon-wafer-pricing and defect-density data from foundries and trade groups, package-pricing data from packages, and test- and assembly-cost data from various vendors. The InCyte economic engine's database stores that data. "We take the output of our InCyte tool, which provides technical chip estimation for die size, power consumption, and number of pins, and combine that data with the new economic data to produce this final packaged-chip cost," says Traidman.

The engine also has a lifecycle-analysis feature that allows designers to forecast and account for mask re-spins, increasing yields, and decreasing wafer and package costs. Traidman says that Giga Scale will eventually improve the tool to allow users to analyze whether they should implement their designs in FPGAs, structured ASICs, or tradition-

al cell-based-ASIC fabrics. The economic engine is available as a \$2000 upgrade to InCyte. InCyte is available as a free download at www.chipestimate.com.

-by Michael Santarini▶Giga Scale Integration, www.gigaic.com.

### Embedded DSP simplifies programming

Sheldon Instruments' recently released SI-C6713DSP-PC104p embedded DSP board in the PC/104-Plus form factor targets real-time test, measurement, and digital-control applications. With a typical power consumption of only 2.25W, the board features the latest 300-MHz TMS320C6713 DSP from Texas Instruments and as much as 256 Mbytes of SDRAM. An expansion site for a family of multifunction I/O modules extends the DSP power with as many as 64 analog inputs and 16 analog outputs; a timing interface with two digital synthesizers and four counters; and a digital interface that comprises 32 bits of general-purpose I/O, two quadrature encoders, two frequency counters, and two PWM outputs.

The board comes with DSP-software libraries that enable system engineers to directly program their DSP systems in Visual

Basic or National Instruments' (www.ni.com) LabView. However, for those who require custom development, the conventional C/C++-based tools have source-code-distribution support. Prices for the SI-C6713DSP-PC104p board with a 300-MHz DSP and 64 Mbytes of SDRAM start at \$1985, and prices for I/O modules start at \$595.

-by Warren Webb **Sheldon Instruments**,

www.sheldoninst.com.

Designers can easily program the SI-C6713DSP-PC104p board in LabView and Visual Basic. The board incorporates the TMS320C6713 DSP operating as fast as 300 MHz.

### FEEDBACK LOOP

"Many (software engineers) are actually other types of engineers that became involved with programming in school or on the job through necessity. Often facing a time crunch, they write only enough code to make the project work, rarely giving any thought to quality

Joseph Travis, in *EDN*'s Feedback Loop on www.edn.com/article/CA601846. Add your comments.

### Physical guide routes optical guide

Even optical fibers, although relatively rugged, may still need some support and protection when designers cram them into today's tight and crowded boxes and systems. The OFFGS (optical-fiberflexible-guide system) from Richco Inc provides the needed routing and channeling for 250- and 900-micron fibers. The flexible quide lets designers snake the fiber around the pc board and within the box and provides consistent placement and basic protection.

According to Cheryl Cummins, marketing manager at Richco, the OFFGS is available in a flat style for mounting directly to the pc board and with support posts that raise it above the pc board, so that it can go over ICs and other obstructions. A standard OFFGS piece measures 6.5 in. (16.5 cm) long and costs about \$2.

−by Bill SchweberRichco Inc, www.richo-inc.com.

Keep that optical fiber well-behaved and constrained within your peboard-based product with a flexible guide from Richco.

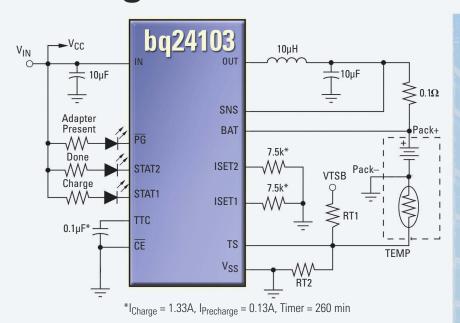

# Integrated FET Switch-mode Charger

### Synchronous, High-efficiency 2-A Switch-mode Lithium-Ion Charger Fits in 3.5 x 4.5 mm<sup>2</sup> QFN Package

The **bqSWITCHER**, the industry's first family of synchronous switch-mode battery charger ICs with integrated FETs, provides faster and cooler charging in portable applications. Ideal for high-efficiency charger designs with up to three Lithium-lon battery cells in series, the bq241xx enables a small and simple solution by requiring only a few external components.

### **bqSWITCHER** Products

| Device                                                          | Charge Regulation Voltage               | Application       | Price* |

|-----------------------------------------------------------------|-----------------------------------------|-------------------|--------|

| bq24100                                                         | 1- cell (4.2 V)                         | Standalone        | \$2.10 |

| bq24103                                                         | 1- or 2- cell selectable                | Standalone        | \$2.20 |

| bq24105                                                         | Externally programmable (2.1 to 15.5 V) | Standalone        | \$3.50 |

| bq24113                                                         | 1- or 2- cell selectable                | System-controlled | \$2.20 |

| bq24115                                                         | Externally programmable (2.1 to 15.5 V) | System-controlled | \$3.50 |

| *Suggested resale price in U.S. dollars in quantities of 1,000. |                                         |                   |        |

### **NEW**

### ▶ Applications

All 1-, 2- and 3-cell Li-lon battery-powered applications:

- Portable DVD players

- Portable media players

- Handheld devices

- Industrial equipment

- Medical equipment

### **▶** Features

- Charges 1, 2 or 3 Li-lon cells

- Synchronous 1.1-MHz PWM converter

- Highly integrated:

- 2-A charge FETs

- Reverse-blocking diode

- Thermal shutdown

- Battery management features maximize capacity, cycle life and safety:

- Accurate voltage and current regulation

- Charge conditioning, status and termination

- Battery detection

- Safety timer

- Temperature monitoring

### ▶ Packages

- 20-pin 3.5 x 4.5 mm<sup>2</sup> QFN

- Lead-free, RoHS-compatible

www.ti.com/bq24100 ° 800.477.8924, ext. 24100

### Emulators speed event-based verification

haras Systems Inc has released two new emulator systems that use multiprocessor SOCs (systems on chips). The singleuser Hammer S-Class emulator has a capacity of 16 million gates and targets hardware designers needing to speed event-based verification. The multiuser Hammer M-Class emulator has a 64 million-gate capacity and targets hardware engineers who want to verify their designs, and, through the new Virtual Connect add-on, software engineers, wishing to get a jump on software development. Richard Curtin, senior vice president of marketing and business development for Tharas, says that the two new systems improve on the company's previous offering, the Hammer 100 system, on just about all fronts.

Whereas the Hammer 100 used 128 processors, had a 32 million-gate capacity, and ran an 8 million-gate design with a testbench operating at 4.5 kHz, the new S-Class uses 1024 custom processors, has twice as many gates, and runs the same 8 million-gate design at 50 kHz. The M-Class has 4096 processors, a fourfold gate increase, and the ability to run the same 8 million-gate design at 200 kHz.

Curtin attributes the speed and capacity improvements to the company's placing 32 of its Hammer 100 custom processors on one SOC. This approach increases the capacity and exponentially speeds the emulators and allows Tharas to offer the systems in a form factor the size of a big toaster. Tharas also custom-designed the instruction set to handle Boolean operations for simula-

tion. Custom instruction-set simulation speeds emulation. The company has also worked extensively on the compiler to help users quickly load their designs onto the emulator systems. Curtin claims a 50 million- to 60 million-gate compilation time. The emulators accept Verilog- and VHDLdesign files; assertions in OVL (object-verification language), OVA (Open Vera assertion), and PSL (property-specification language); and testbenches in Verilog, VHDL, or C/C++.

Tharas also offers a software add-on that allows embedded-system engineers to get a jump on software development. The company's Virtual Connect add-on has three flavors of software models targeting popular market segments: the Virtual-PC platform for graphics applications, the Virtual-Net for networking applications, and Virtual-3G for wireless applications.

Curtin says that most users are designing ASICs with 5 million to 6 million gates. "A 16 million-gate system, such as the S-Class, should cover most design groups for the next couple of design projects," he says, arguing that manufacturers will realize the value of the emulator for its increased speed versus simulation over the life of the system. Prices for the Hammer S-Class start at \$200,000 for a 4 million-gate configuration, and prices for the M-Class start at \$750,000 for a 32 million-gate configuration. Tharas also rents its emulators. Price of an S-Class rental in an 8 million-gate configuration starts at \$21,000 per month. Price of an M-Class rental in a

### Module enables graphical embedded programming

National Instruments recently announced an embedded-development module for its popular LabView software that extends graphical programming to any 32-bit embedded processor. With the module, designers can describe algorithms and program their applications using LabView's graphical data-flow language. In addition, LabView's graphical front-panel controls and indicators help engineers quickly and interactively experiment and debug their embedded code.

The LabView embedded-development module includes more than 400 analysis functions for signal processing, linear algebra, curve fitting, statistics, and calculus. The module also features a structure for integrat-

The new LabView embeddeddevelopment module provides designers with a graphical approach to custom embeddedsystem development. ing I/O drivers and boardsupport packages to take advantage of specific processors. Designers can develop their applications using the LabView graphical environment and then automatically generate C code to integrate with their chosen processor tool chains.

James Truchard, PhD, chief executive officer and co-founder of National Instruments, says, "The evolution of LabView beyond the PC will open embedded-system design to

an entirely new class of developer-a more mainstream population of scientists and engineers." Prices for the module start at \$9995.—by Warren Webb

National Instruments, www.ni.com/embedded.

32 million-gate configuration starts at \$52,000 per month. Prices for the Virtual Connect add-on start at \$75,000. —by Michael Santarini ▶Tharas Systems, www. tharas.com.

### **FEEDBACK LOOP**

"I have this idea that I can apply engineering design to stock prices as though they were signals and make a living that way. Hey, if it works, my income won't be limited, and I can't be outsourced!"

Anonymous, in *EDN*'s Feedback Loop on www.edn.com/article/CA529820. Add your comments.

### **Intersil Battery Charger ICs**

Intersil High Performance Analog

# Don't Get Burned by Cheap Imposters

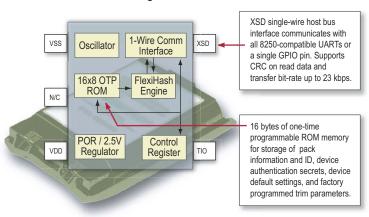

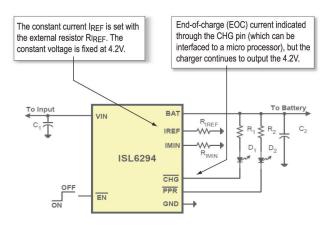

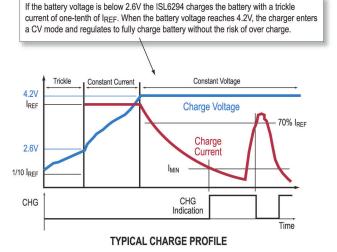

Protect your designs from counterfeit battery packs with Intersil's ISL6296. We've integrated our FlexiHash™ technology to deliver a simple, robust and inexpensive battery authentication solution for 1-cell Li-lon/Li-Polymer or 3-cell NiMH series battery packs.

Intersil's ISL6296 offers the same level of effectiveness as other significantly more expensive, high maintenance, monetary-grade hash algorithm and authentication schemes. This device supports a wide range of operating voltages and is customized for low-cost applications.

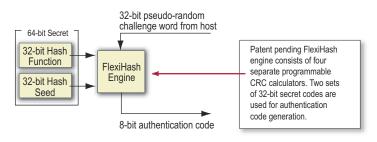

### ISL6296 Functional Block Diagram

### **Device Authentication Process**

### **Key Features:**

- Patent pending challenge-response authentication scheme using 32-bit challenge code word and 8-bit authentication code.

- Fast single-step authentication process

- Supports 1-cell Li-lon/Li-Polymer and 3-cell series NiMH battery packs (2.6V-to-4.8V operation)

- Compatible for use with serial ports offered by all 8250-compatible UARTs or a single GPIO pin

- "Zero Power" sleep mode after bus inactivity time-out period

- 64-bit user-programmable secret for security

- Can also be used in a variety of accessories such as printer ink cartridges where authenticity needs to be verified.

- Variety of packages available including SOT-23-5, chip scale or unpackaged die

Datasheet, eval kit with USB interface, free samples, and more information available at www.intersil.com/edn

Enter 11 at www.edn.com/info

### Q&A

### Todd Westerhoff

### EDA industry should use what it sells

s a high-speed-design manager for Cisco Systems Inc and a former product manager for Cadence Design Systems, Todd Westerhoff feels the pain of EDA customers he used to sell to and advise. He has 25 years of experience in modeling and analyzing electronics systems. Currently, he and his team of 10 focus on signal integrity and

support other design groups at Cisco. Westerhoff earned a bachelor's degree in electrical engineering from the Stevens Institute of Technology (Hoboken, NJ). He vented his frustrations about EDA tools in an interview after a recent vendor panel sponsored by the EDA Consortium.

### What do you do at Cisco?

We use simulation tools to model the behavior of chips and the way we interconnect them at the board level. The limiting factor is that the speed of light is too slow. Circuits are switching so fast that the way a signal propagates is like a wave front. We can no longer consider circuits as lumped elements but rather as distributed structures like a wave.

### Where does EDA come into the picture?

In the past, you'd put these boards onto an oscilloscope or analyzer, but we use off-the-shelf simulation tools to increase the chance of first-pass success. The cost of mistakes in board design is prohibitive. The problems we face are so complex, you can't fix them simply by trial and error. We have to use simulation tools before we "fab" out the board.

### Why do EDA tools fall short?

The things we are trying to do, such as determine how an ASIC works

with other chips, is a fantastically complex problem. It requires multiple tools to predict the board's behavior. Even the vendors that say, "We have a full solution" don't cover the myriad details associated with modeling and manufacturing the board. The problem of building something and bringing it into manufacturing has a million angles.

### Why does this problem evoke so much emotion?

I don't know if I'd [sound off strongly in a public forum] again. But sometimes you have to shake people up to get them to do things differently. I've been saying [EDA companies should use their products in actual design] for seven or eight years, and, obviously, not a lot of people are listening. We spend a lot of time and money on getting these tools to work correctly. I don't know anybody who says their relationship with the EDA industry is a walk in the park. But we'd be a lot better off if these tools were tested in a real-world situation.

### How did your transition from vendor to customer influence your thinking?

When I got out of college, I spent 10 to 12 years as the guy marketing analog and digital simulators. Then I went out as a consultant using EDA tools, and it was a real eye opener. Instead of selling tools, I went to make a living using the tools. Many users never develop the comprehensive understanding of the tool that the vendors expect. User understanding of the tool is uneven, so everybody's perception of what needs improvement is different. The tool becomes difficult and complex to manage. They are big and complicated with many options. The user is saying "I just want to solve this problem." What grows out of that is you have tools that don't work or solve problems.

When I got into EDA around 1983, the paradigm was that, if you could get a computer to do what you wanted, you would be thankful. That [mindset] has never gone away with [EDA]. People tend to look at the problem from their own perspectives. It all changes when you turn around and try to use it, but if you don't use these things, you're not going to be able to perfect them. They're like race cars. You have to go to the track and beat them to death, or you're not going to win. It's also kind of like being in battle where everything is changing and going on around you. The last thing you need is to be in battle with tools that are unpredictable.

### How do you cope?

It's a constant problem and one we've learned to live with. The fascinating

thing is that some of the things we thought were trivial are big deals, and the things we thought were simple rough edges turn out to be big factors.

### Please give an example.

When I was a vendor, this schematic editor had all these fancy functions. Users came back and said that to put a component down and rotate it took seven mouse clicks, whereas our competitor's product required two. Vendors need to get things done repetitively rightnot close, but right. You need to nail it. If it's something a user is going to do several hundred times a day, it is going to drive him crazy. And, if you're going to nail it, you've got to use it.

We can ask [a vendor] to add another bell or whistle to a simulator. [They say], "Here's this collection of capabilities. If we change it all around, maybe we can give them that feature." They might say, "We can't quite do this, but we can do something like it." That could be in 12 to 18 months, and compromises get made along the way. In the meantime, the technology moves on.-by John Dodge

For an extended version of this interview, go to www.edn. com/050707/pg&a.

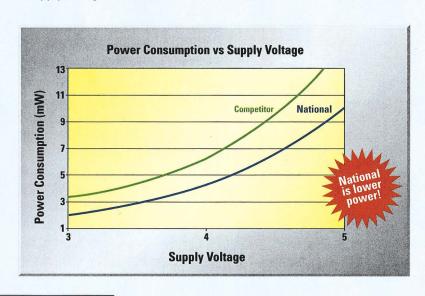

Thanks to our low-voltage, low-leakage yet high-speed designs,

Fujitsu is the preferred choice in power-conscious MCUs.

Glucose monitors, home theatre remotes, security systems,

and thermostat controls are just a few examples of the

hundreds of applications where our new, expanded 8-bit MCUs have found a home. But this preference

is no accident. We understand better than anyone

the price, performance and space challenges faced by engineers, and the end result is

a design architecture unrivaled in its power and

flexibility. What's more, working with Fujitsu

offers world-class manufacturing and a

proven track record of reliability.

For more on Fujitsu's MCUs and our industry-leading solutions,

visit www.fma.fujitsu.com/mcuad

or call (800) 866-8608.

### **MICROCONTROLLERS**

- 8-bit, 16-bit, 32-bit MCUs

- Up to 768 KB embedded Flash memory

- Up to 5 channel UART

- Low-power modes

- DC/AC motor, inverter control modules

- Dedicated DSC application specific controllers

- LPC bus, PS2 interface, keyboard controller with multi Li-ion battery management

- A/D, D/A, LCD controllers/drivers and timers

- Full-featured ICE and integrated development environment available

Bringing solutions to your business is Vu Lac, Technical Sales Manager for Fujitsu Microelectronics.

THE POSSIBILITIES ARE INFINITE

www.fma.fujitsu.com

### **MGLOBAL DESIGNER**

### WiCon panel opines on state of wireless standards

t the WiCon (Wireless Connectivity) World show in London in May, Mike McCamon, executive director of the UWB Forum (www.uwbforum.org), described as "an utter mess' the current situation of competing personal-wireless-connectivity standards. Partially giving rise to the description was the Bluetooth Special Interest Group's (www.bluetooth.com) May 2005 announcement that it intends to work with developers of UWB (ultrawideband) technology to "combine the strengths of both technologies." McCamon likens the proliferation of standards to the situation in wired networking around 1990. He looks toward a similar simplification in the same way that IP (Internet Protocol) came to dominate networking technology, anticipating that the wireless industry should be able to "clean up" the situation.

The UWB Forum stands on one side of the continuing UWB-standards wrangle, and the MBOA (Multiband OFDM Alliance) stands on the other. Nevertheless, Kursat Kimayacioglu, MBOA marketinggroup member and director of wireless business development for the connectivity-busi-

ness line at Philips (www. philips.com), echoes the sentiment. He looks to a more unified wireless environment in which the Bluetooth profile becomes just one of a number using the UWB-air interface.

The show provided a snapshot of progress toward functional UWB in its native mode; Freescale (www.freescale. com) operated a streamingvideo demonstration with a claimed 100-Mbps link spanning 15 to 20m. This demonstration employed the first multichip implementation of its direct-sequence UWB silicon, and the company promises further integration. Visitors could also see file transfer over a wireless-USB link using first silicon of Staccato Communications' (www.staccato. communications.com) singlechip all-CMOS offering. Staccato envisages the technology's reaching the market on a time scale that would see external adapters for file transfer from PC to external hard drive early in 2006 and reaching high-end mobile-phone platforms in 2007.

> -by Graham Prophet, EDN Europe

▶Wireless Connectivity World, www.wiconworld.com.

### BITS & PIECES

➤ Yokogawa Electric Corp (www.yokogawa.com) of Japan has released the DL9000 series digital-oscilloscope platform for the 1-GHz band. For more, see www.edn.com/050707p1.

Description Descr

### FPGAs implement high-end image-processing applications

New FPGAs with more DSP resources and embedded-processing capabilities have made the global image-processing market more competitive. According to Rahul V Shah, ASIC manager at elnfochips, an ASIC-design and -verification-services provider, designers can offload software-implemented algorithms, such as DCT, static Huffman, AES (Advanced Encryption Standard), color-space conversion, and gamma correction, to FPGA hardware. He claims that this approach improves system performance. Shah also notes that the conventional manner of implementing algorithms by software limits performance due to serial data processing. Increasing frequency beyond certain limits causes system issues. FPGAs have flexible architectures and dedicated DSP blocks. Coupling these benefits with parallel processing strikes a proper balance in system performance and cost. FPGAs extend the flexibility to reprogrammability, resulting in a quick turnaround time.

According to Shah, parallel processing in hardware is impossible because hardware processing can execute instructions only one at a time. "If you want to run a DCT along with static Huffman with the same processor, one process at a time will execute," he says. "However, in hardware, because everything runs in parallel, you can have DCT and SHF [super-high-frequency] running in parallel at the same time without any performance hit." He adds that FPGAs provide the flexibility to upgrade to new standards and reprogram devices. For example, you can modify any system-level application to DDR and then move to DDR-2.

Designers can also reshuffle images to create applications, such as video cell phones, set-top boxes, LCD projectors, keyboards, videos, mice, and digital cameras and camcorders, among others. "Implementing DSP algorithms for image-processing blocks, such as DCT, AES, and static Huffman, requires a huge amount of memory, multiplier, and accumulator blocks," says Shah. For example, a DCT at 133 MHz can take as many as 64 multiplication and addition operations. Designers can map these multipliers onto the hardware to perform multiplication and addition operations, rather than do it sequentially in software. Static Huffman and AES cores have high memory requirements for storing coefficient values and performing mathematical operations on incoming data. Handling these operations in software slows down system performance and overloads the CPU. Offloading these tasks to the hardware means that the memory stores the image, and the CPU performs other control operations.

Implementing a dynamic Huffman algorithm in hardware would be a bad idea, because the algorithm requires dynamic calculations, which need a large amount of hardware, so proper partitioning between hardware and software is necessary. This approach is more cost-effective and provides better performance than running the algorithm in software.

-by Pradeep Chakraborty, EDN Asia

▶eInfoChips, www.einfochips.com.

We think electronic design can never be too innovative or efficient.

What do you think?

YOU ENVISION a new way to empower your customers. You strive to continuously improve your designs and settle for nothing short of excellence. We think alike.

AT INFINEON, we never stop thinking about developing and perfecting innovative semiconductors for automotive, communications, and memory markets. Our passion for providing you the most advanced technology is evidenced by over 40 R&D centers, an annual R&D investment of \$1.5 billion, the 41,000-plus patents we now hold, and the \$8.9 billion revenues that ranks us among the world's top five semiconductor companies.<sup>1</sup>

DO YOU THINK you can break new ground with your next design? Visit www.infineon.com/us to see how our Smart Chip solutions can make your design even more innovative.

www.infineon.com/us

### **Sensing** Optimization

### **High Performance Analog Solutions**

Power management and signal chains demand a system approach – that's why Avnet Electronics Marketing and National Semiconductor together are such a powerful combination.

- performance with overall efficiency

- Collaborative engineering support from conceptual design through volume manufacturing

- System level expertise to assist in determining the right architecture and products for your application

- versed in National's technology and tools

- Avnet PartBuilder™ and online technical training

- Temperature sensors, operational amplifiers and A/D

- Solutions sample kits to assist you in your designs

Whether you're working on a portable, handheld, security, medical or other analog design, let Avnet EM help you solve your power and signal design challenges and get your application up and running.

go to avnet.national.com

- Factory-trained Field Application Engineers well

- Web-based design tools like National's WEBENCH®,

- converters that can optimize system performance over a wide range of operating conditions

For sample kits and design tools,

### National Semiconductor The Sight & Sound of Information

Enabling success from the center of technology™

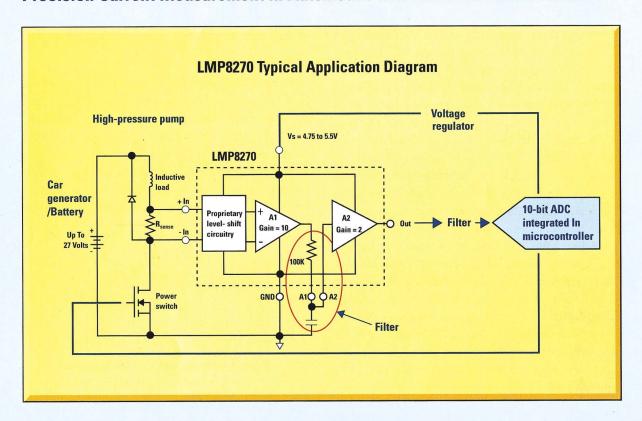

### **Sensing Solutions: Part III**

### **SENSING IN MISSION-CRITICAL APPLICATIONS**

Part three of this three-part series on sensing solutions looks at high performance sensing systems, such as those used in ultrasound or MRI equipment. Susceptible to the slightest variations in power, noise, and signal latency, high performance sensing systems must deliver exceptional accuracy at extreme data rates — even a small error may be the difference between detecting cancer or not.

To read this case study. go to avnet.national.com

### **Delivering Exceptional Accuracy** at Extreme Data Rates

This month, industry expert Nicholas Cravotta explores the unforgiving nature of working with high performance sensing systems in mission-critical applications, including:

- The importance of power supply stability and how to achieve it

- Managing high-speed sensor data flow through aggregation while minimizing signal skew

- Implementing effective signal conditioning to scale sampling voltage and attend to phase differences without compromising signal integrity

- Handling EMI and noise to maintain signal resolution and accuracy

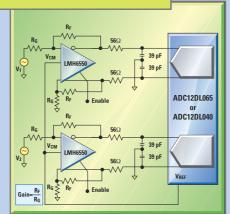

### **Typical Application**

The ADC12DL040 and ADC12DL065 A/D converters are ideal for use in ultrasound, imaging, instrumentation, and sonar/radar applications.

### PRODUCT SPOTLIGHT:

### ADC12DL040

Dual 12-Bit, 40 MSPS, 3 V, 210mW A/D Converter

### ADC12DL065

Dual 12-Bit, 65 MSPS, 3.3 V, 360mW A/D Converter

### LMH6722

Quad Wideband Video Op Amp

### LMH6502

Wideband, Low Power, Linear-in-dB Variable Gain Amplifier

### LMH6503

Wideband, Low Power, Linear Variable Gain Amplifier

### LMH6504

Wideband, Low Power, Variable Gain Amplifier

900 MHz Voltage Feedback Op Amp

### LMH6550

Differential, High Speed Op Amp

### LMV7219

7 nsec, 2.7 V to 5 V Comparator with Rail-to-Rail Output

### **CLC018**

8 x 8 Digital Crosspoint Switch, 1.485 Gbps

### SCANSTA476

Eight Input IEEE 1149.1 Analog **Voltage Monitor**

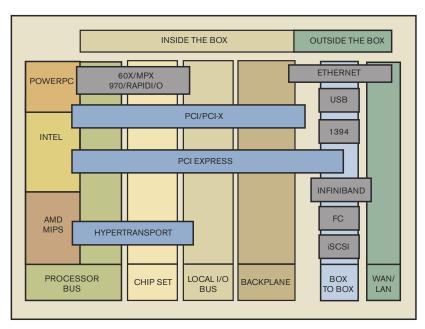

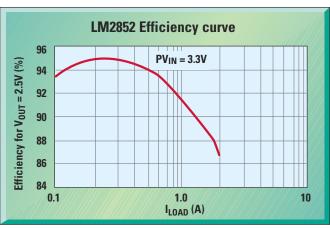

### LM2852

2 A 500/1500 KHz SIMPLE SYNCHRONOUS™ Buck Regulator

1 800 332 8638

### BY BONNIE BAKER

### One in a million

omparing devices from different manufacturers can be difficult not only at the bench, but also at the beginning of your investigation. If you start with the product data sheets, sometimes specification names don't match specification units of measure. In these cases, simple translations are useful in differentiating styles of units of measure.

You can glance at the far-right column of the specifications table within ADC data sheets and find the specification units of measure. The most

common ADC dc units are least-significant bit (LSB), full-scale range (FSR), percentage of FSR, and number of bits (n). Some of the ac specification units are decibels for the signal-to-noise ratio (SNR) or the signal-to-noise-and-distortion (SINAD) ratio. These units of measure are standard parts of numerous converter data sheets, but the new, less-familiar parts-per-million (ppm) unit also appears in converter data sheets.

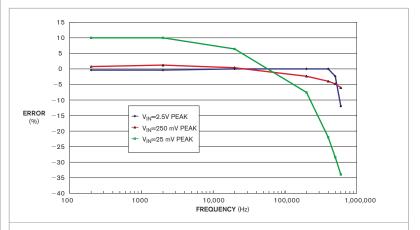

Note that the parts-per-million unit of measure usually appears in the 16-bit or higher resolution ADC data sheets. The fundamental questions you might ask are: What does this specification unit of measure mean to converter users, and why do the higher resolution converters usually have this unit of measure?

In data sheets for lower resolution converters, percentage of FSR appears as a unit of measure. Many converter manufacturers replace percentages with parts per million. This scenario is usually necessary if a percentage specification has too many zeros. For instance, say the gain error of a 12-bit ADC is  $\pm 2.5\%$  of FSR. If you change this specification to parts per million, it becomes ±25,000 ppm of FSR. You make this change by moving the decimal point four places to the left. This example shows an impractical conversion because of the high number of zeros, which makes the specification difficult to read. In contrast, say the gain error of a 24-bit converter is  $\pm 0.005\%$  of FSR. A more legible representation of this specification is  $\pm 50$

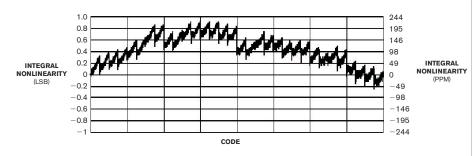

Figure 1 Converter-performance specifications can use either least-significant-bit or parts-per-million units. The two are mathematically equivalent but require that engineers pay attention to the conversion factor.

ppm of FSR. When is one representation better than the other? The breakeven point seems to be at less than 0.1% or at greater than 1000 ppm.

You can also use parts-per-million units to replace least-significant-bit units (Figure 1). A typical dc specification, such as integral nonlinearity for a 12-bit SAR converter, is  $\pm 1$  LSB of FSR. If the FSR of this converter is 5V, the least-significant-bit size is 1.22 mV. 1 LSB equals the converter's FSR divided by number of bits, or FSR/212=1 LSB. The specification number becomes more cumbersome with higher resolution converters. As an example, a typical integral-nonlinearity specification for a 24-bit converter of ±15 ppm of FSR translates to an error of ±251 LSB of FSR. If the FSR of this converter is also 5V, the least-significant-bit size is 298 nV. To return to the original parts-per-million value, divide the least-significant-bit error by the converter's number of bits and multiply by 10<sup>6</sup>.

The conversion from percentage or least-significant bit to parts per million is akin to the conversion from meters to inches, but the mathematics is more forgiving. Although this concept seems elementary, you would be surprised at how many engineers shy away from these representations on the units of measure. The fact that the units of measure in the right column seem to be unrelated from manufacturer to manufacturer discourages many people who compare competitive data sheets. But, in this situation, simple mathematics can put all of the products that you are evaluating onto the same playing field.**EDN**

### MORE AT EDN.COM

→ Go to www.edn.com/050707bb and click on Feedback Loop to post a comment to this column.

Bonnie Baker is the author of A Baker's Dozen: Real Analog Solutions for Digital Designers. You can reach her at bonnie.baker@microchip.com.

# SIGNAL PATH designer

Tips, tricks, and techniques from the signal-path experts

No. 102

| Feature Article1-7         |

|----------------------------|

| Precision Amplifiers2      |

| 1 MSPS ADCs4               |

| Current-Sensing Amplifier6 |

| Design Tools8              |

### **Maximizing Signal-Path Performance**

— By Chuck Sins, Applications Engineer

**Precision Signal Path**

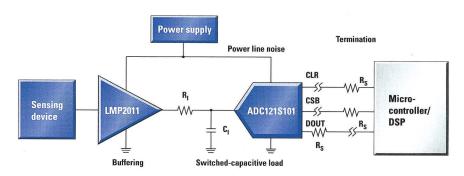

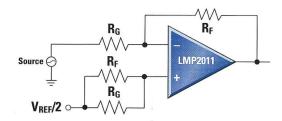

The signal path offers many opportunities for the system designer. In the analog-to-digital converter (ADC) signal path, making good design choices in buffering a sensing device, charging the switch-capacitive input of an ADC, and minimizing noise sources will maximize performance. All of these examples will be addressed in this issue of the Signal Path Designer.

### **Buffering a Sensing Device**

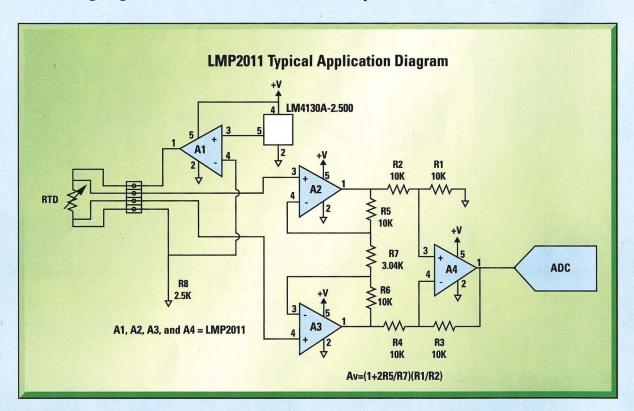

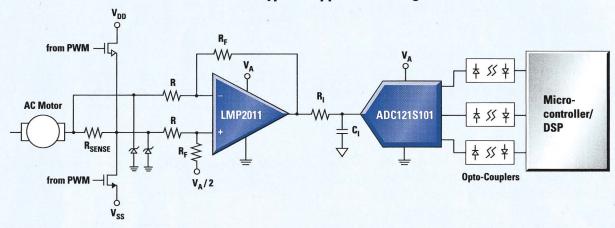

When a sensing device is unable to drive the capacitive load of an ADC, it can be buffered with an operational amplifier (op amp). Since many applications require operation from a single supply, it is important to select an op amp that operates at the same voltage as the ADC. While sharing supply voltages helps reduce system complexity and cost, supply voltages place constraints on the input and output capability of the op amp. For ADCs such as the ADC121S101 where the reference voltage (V<sub>REF</sub>) is both the supply voltage and the reference, op amps such as the LMP2011 with rail-to-rail output (RRO) capability are preferred. The LMP2011 with RRO capability allows the system designer to utilize the full dynamic range of the ADC, providing access to all of the output codes.

Once an op amp with suitable input/output capabilities has been selected, its gain bandwidth needs to be considered. For cases where the stimulus source's maximum output is less than V<sub>REF</sub>, gain may be required from the buffering stage. The gain bandwidth product (GBWP) of an op amp specifies its

### **NEXT ISSUE:**

**High-Speed Signals,** Clocks, and Data Capture

### High Precision-Rail-to-Rail Output Amplifiers

### **Delivering High Precision Over Time and Temperature**

### **LMP2011/12/14 Key Features**

### **System Benefits**

- 60  $\mu$ V V<sub>OS</sub> max over temp (- 40°C to +125°C )

- Offers high accuracy measurements with continued accuracy over temperature

- Low voltage noise (35 nV/ $\sqrt{\rm Hz}$ ) and no 1/f

- Increase signal accuracy during low frequency measurements

- High CMRR (130 dB), PSRR (120 dB)

- High accuracy across voltages

- Gain (130 dB) and 3 MHz GBW product

- Wide frequency range at higher gains

### SIGNAL PATH | designer

### **Maximizing Signal-Path Performance**

bandwidth (-3 dB frequency) when configured as a unity gain amplifier. Since GBWP remains constant for a given op amp, a closed loop configuration with a gain of  $A_{CL}$  lowers the bandwidth by a factor of  $A_{CL}$ :  $B_{W} = GBWP$

For example, the LMP2011 with a GBWP of 3 MHz will have a bandwidth of 300 kHz when configured with an A<sub>CL</sub> of 10 V/V.

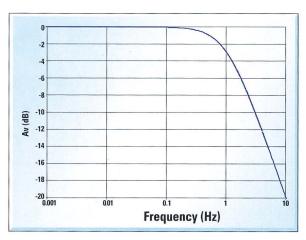

Because the closed-loop bandwidth is the -3 dB frequency of the amplifier, it is the frequency where the amplifier output is 70.7% of its input value. So at the -3 dB frequency there is a 29.3% error in output amplitude. Errors in ADCs are measured in units of least significant bits (LSBs). One LSB is defined as V<sub>REF</sub>/2<sup>n</sup> where V<sub>REF</sub> is the reference voltage and n is the ADC resolution. For example, 1 LSB of an 8-bit ADC is V<sub>REF</sub>/256. For a system requiring 1/2 LSB of accuracy from its ADC, the input stimulus must have gain accuracy of (1-1/2<sup>n+1</sup>) or 99.8% for an 8-bit ADC. To guarantee that the op amp has sufficient gain accuracy for a given system requirement, it is necessary to calculate the maximum operating frequency  $(f_{max})$  for the op amp. This is accomplished by approximating the frequency response of an op amp to be that of a single pole filter. The curve shown in *Figure 1* has the gain  $(A_V)$ and -3 dB frequency (f<sub>o</sub>) normalized to 1.

The expression for this curve is

$$A_{V} = \frac{1}{\sqrt{1 + (f)^{2}}}$$

.

or solving for f,

$$f = \sqrt{\frac{1}{A_v^2} - 1}.$$

To achieve 1/2 LSB of error from an 8-bit system, the normalized  $f_{max}$  of an op amp is

$$f = \sqrt{\frac{1}{(0.998)^2} - 1} = 0.062$$

Therefore, for an 8-bit ADC with a 1/2 LSB accuracy requirement, the op amp's effective bandwidth is 0.062 x GBWP. The LMP2011 with a GBWP of 3 MHz would have an effective bandwidth of 186 kHz when configured for unity gain. The effective bandwidth is further reduced if a gain greater than unity is required. The normalized  $f_{\text{max}}$  for

Figure 1. Op-Amp Frequency Response

$^{1}/_{2}$  LSB of error for ADCs of various resolutions can be calculated as:

Normalized  $f_{max} = \sqrt{\frac{1}{\left(1 - \frac{1}{2^{mil}}\right)^{2}} - 1}$ .

### Transferring Charge to a Switched-Capacitive Load

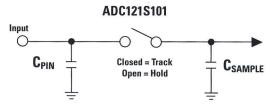

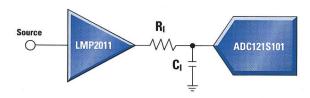

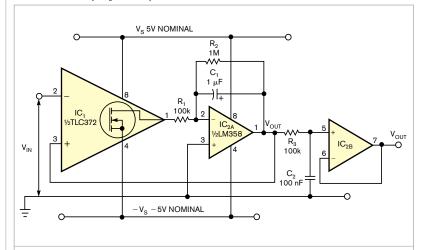

The op amp was added to the ADC signal path to drive the capacitive load. However, the ADC's input is a switched-capacitive load (see Figure 2).

Figure 2. ADC121S101 Input

The ADC121S101 in "hold" mode has an input capacitance, C<sub>PIN</sub>, of less than 4 pF, and in "track" mode has an input capacitance, C<sub>SAMPLE</sub> plus C<sub>PIN</sub>, of less than 30 pF. To minimize the error caused by the changing input capacitance, a capacitor (C<sub>I</sub>) is connected from the input pin to ground. The C<sub>I</sub>, which is much larger than the input capacitance of the ADC when in "track" mode, provides the current to quickly charge the ADC's sampling capacitor. An isolation resistor is generally added to isolate the additional load capacitance from the op-amp output (see Figure 3).

### Low power, high precision 8/10/12-bit, 1 MSPS ADCs

### **ADC121S101 Typical Application Diagram**

### **ADC121S101, ADC101S101, and ADC081S10 Features (typical)**

- Speed range: 500 KSPS to 1 MSPS

- Integral non-linearity (INL): ±0.4 LSB

- Differential non-linearity (DNL): ±0.5 LSB

- Signal-to-noise ratio (SNR): 72.5 dB

- Signal-to-noise and distortion ratio (SINAD): 72 dB

- . Spurious free dynamic range (SFDR): 82 dB

- Power consumption: 2 mW at 3V

- Supply voltage: 2.7 to 5.25V

### **Family Benefits**

- Guaranteed performance over speed

- · Pin and function compatible family

- Excellent static and dynamic performance

- · Extremely low power

- · Miniature packages reduce board space

### SIGNAL PATH | designer

### **Maximizing Signal-Path Performance**

Figure 3. Quick-Charge Circuit